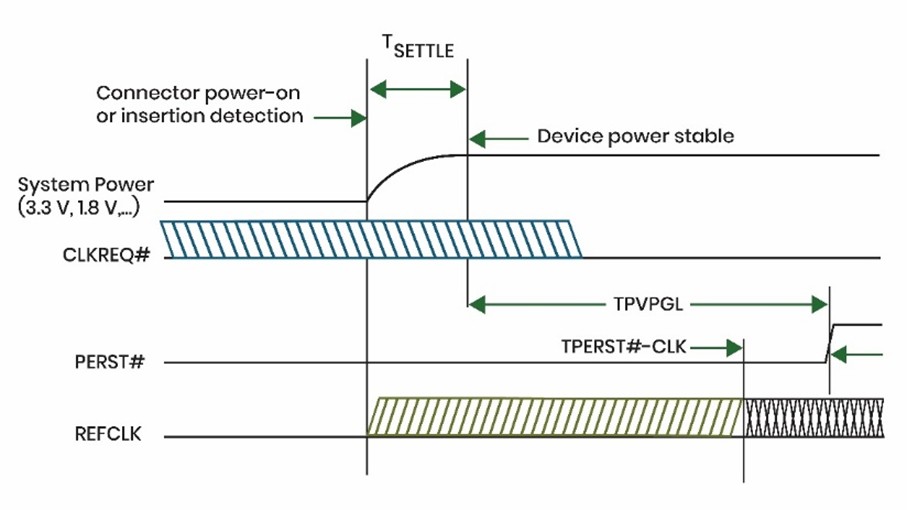

During the power-on sequence of a PCI Express (PCIe) system, the reference clock (REFCLK) and sideband signals may not have reached their required stability or operating tolerance. The PERST# (PCIe Reset) signal is an active-low, open-drain output driven by the Root Complex (RC). It is used to hold the endpoint (EP) devices in reset while the system’s power and clock signals stabilize. The PERST# signal remains asserted (held low) until the RC confirms that the power rails and REFCLK are stable. Once these are within specification, the RC deasserts (releases) PERST#, signaling to endpoint devices that the system is ready to begin PCIe link initialization.

From the endpoint’s perspective, the deassertion of PERST# acts as a global reset release and indicates that power and clocks are valid, allowing the endpoint to start its PCIe link training and initialization process.

To ensure successful link initialization and operation between the Root Complex (RC) and Endpoints (EPs), the following timing requirements must be observed:

Symbol | Parameter | Min | Max | Units | Note |

TPVPGL | Power Valid to PERST# input inactive | Note 1 | ms | 2 | |

TPERST#-CLK | REFCLK stable before PERST# de-assertion | 100 | µs | ||

TFAIL | Power level invalid to PERST# assertion | 500 | ns | ||

TPERST | Assertion time of PERST# | 100 | |||

TPERSTSLEW | Slew rate of PERST# transition to de-asserted | 50 | mV/ns | 3 |

Our team represents a talented, experienced, and highly specialized group of development engineers, sales and marketing specialists. Through many years of direct engineering involvement with our customers, our personnel have developed expertise in wide range of technologies in serial data.

Prodigy Technovations Pvt Ltd

#294, 3rd Floor, 7th Cross, 7th Main, BTM II Stage,Bangalore – 560 076 | India

+91 80 4212 6100

contact@prodigytechno.com

© 2023 Prodigy Technovations. All Rights Reserved

PGY-UFS4.0-PA, UFS Protocol Analyzer is the industry-first working and tested UFS4.0 Protocol Analyzer. It offers protocol data capture and debugging of data across MPHY, UniPro, and UFS protocol layers…