针对 DDR5 串行存在检测 (SPD) 的多通道I3C 总线解码

串行存在检测(SPD)是一种自动获取 DDR3/4/5 内存模块信息的标准方法. 当一个系统接通电源时,它会通过识别不同的硬件组件开始自动配置系统。 串行存在检测(SPD)是 DDR3/4/5 中的一项功能,可使电子系统了解 DDR 内存的详细信息及其定时信息。 DDR3/4 内存模块使用 SM bus提供这个信息。 对于最新的超高速内存,DDR5 使用低压信号(1V)I3C 接口来读取内存详细信息及其定时信息。

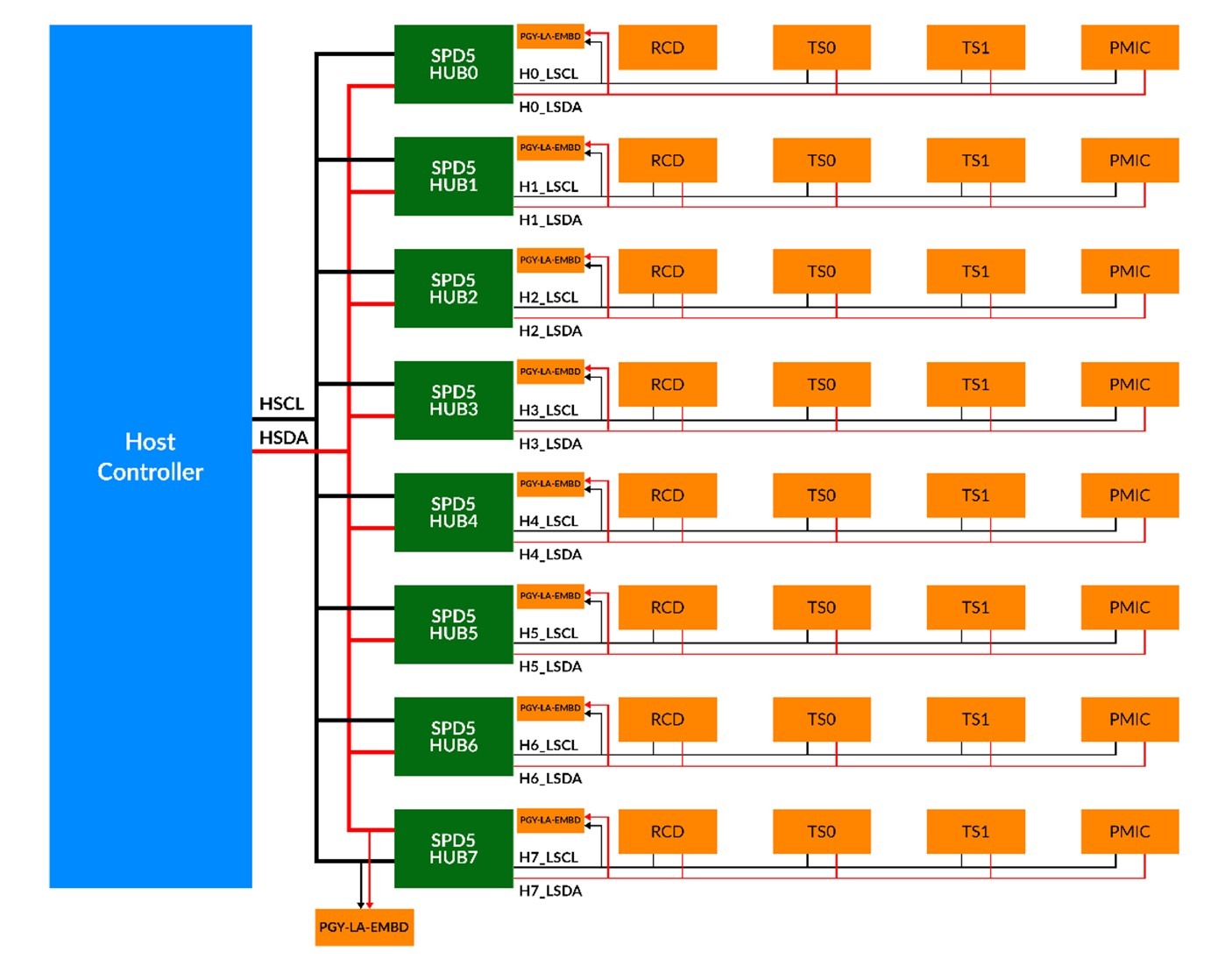

Fig 1. 基于 DDR5 的系统设计中的典型 I3C 总线架构

典型的 I3C 总线结构如图 1 所示. 当主机控制器使用串行存在检测 – SPD5 集线器连接 DDR5 模块 在设计和测试阶段,使用示波器监控这种架构中的所有 I3C 总线是非常具有挑战性的。

调试这些设计的一些关键要求如下:

- 需要能在 1V 信号幅度下工作的逻辑分析仪。

- 需要可以同时获取不同的 I3C 逻辑活动。

- 需要可以对不同的速率运行的I3C总线进行解码,频率从 100KHz 到 12.5MHz 不等

- 监控 I3C 总线中的特定事件

Prodigy Technovations 在现有的逻辑分析仪上开发了业内首个多通道 I3C 解码解决方案。 它具有以下功能:

- 1. 在 1V 信号幅度下识别逻辑电平。

- 2. 同时解码八条 I3C 总线,所有 I3C 总线时间同步。

- 3. 所有 I3C 总线的总线图

- 4. 强大的触发功能

- 5. 异步采样 1GS/s ,可捕捉不同时钟频率的 I3C 协议事件

PGY-LA-Multi-I3C 是一款 16 通道逻辑分析仪 具有以下主要功能

- 1GS/s 异步采样功能

- 8路 I3C 总线解码功能

- 对 I3C 协议数据包内容进行触发

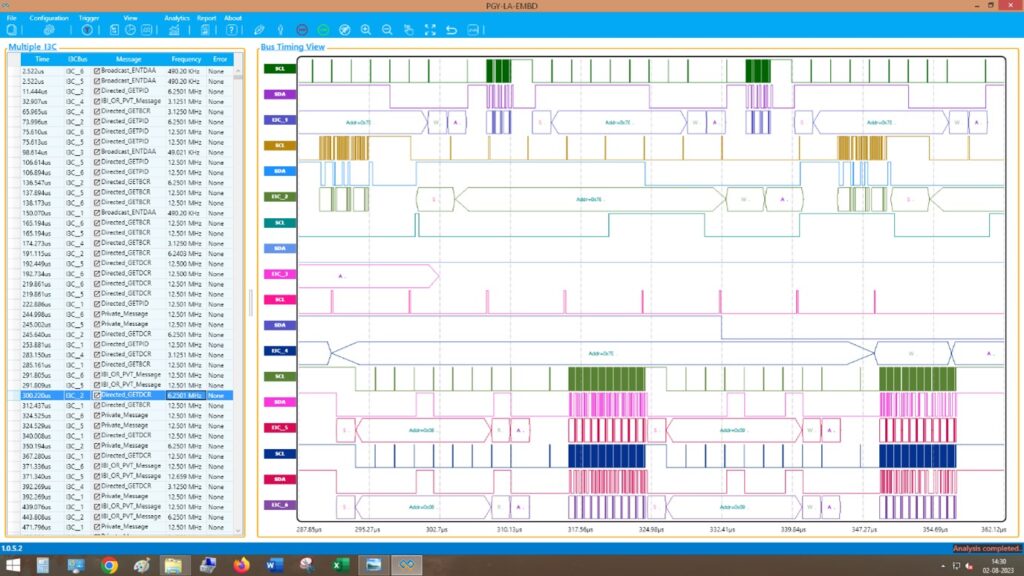

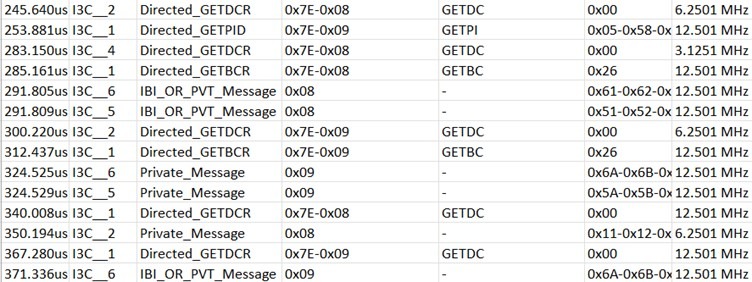

多通道 I3C 协议解码分析结果视图如图 3 所示

Fig. 2. 多通道I3C 信道解码和数字时序图

列表窗口对来自不同 I3C 总线的 I3C 数据包进行解码并显示。 时间戳用于按顺序列出数据包,以便用户了解事件发生的时间。

软件还能通过总线图显示波形. 总线图将显示每个 I3C 数据包的信息,便于调试。

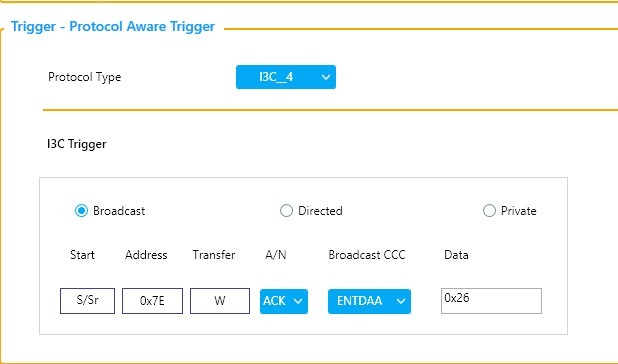

要在特定事件中捕获流量,用户可根据 I3C 协议数据包内容设置触发条件。

更改某些其他 CCC 或私有的触发条件

Fig. 3 I3C 协议触发用户界面

用户可将这些数据导出为 CSV 格式文件. 该数据可通过 Excel 软件查看,以便进一步分析。

Fig4. 在 Excel 软件中导出 CSV

导出的数据包括时间戳、I3C 总线名称、协议数据包内容和运行频率。

PGY-LA-Multi-I3C 提供最全面的解决方案,满足 DDR5 系统对串行外设检测总线的要求。 它可以解码所有八个通道,并提供列表和时序图视图。 导出这些数据的功能使其使用更加方便.

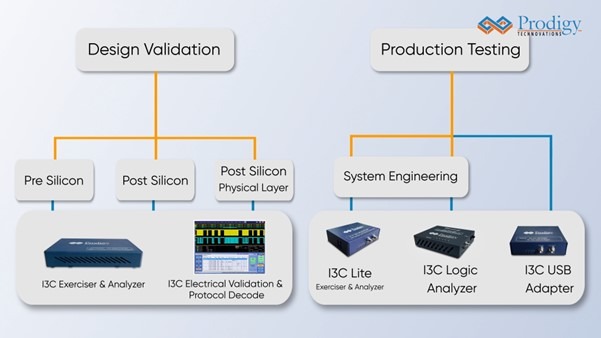

Prodigy Technovations 为开发 I3C 技术提供最全面的解决方案。 Following are our products.

PGY-I3C-EX-PD I3C Protocol Exerciser and Analyzer with optional CTS: https://prodigytechno.com/device/i3c-protocol-analyzer/

PGY-I3C-EX-PD Lite I3C Protocol Exerciser and Analyzer with fixed voltage

PGY-I3C-USB-ADT I3C to USB adapter

Learn more about our comprehensive I3C solutions: https://prodigytechno.com/i3c-protocol-solutions/