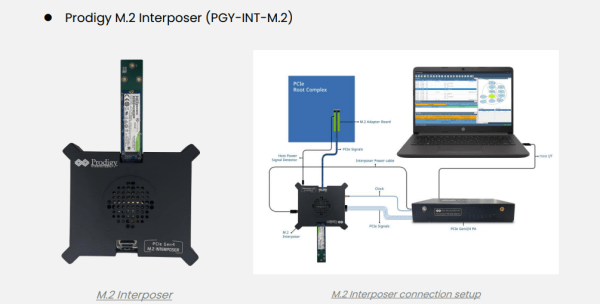

PGY-PCIeGen3/4-PAは、PCIe Gen4速度までのプロトコル解析をサポートするPCIeプロトコルアナライザです。PCIeの設計およびテストエンジニアは、特定のイベントにおける2.5、5.0、8、16GT/sのトレースを簡単にキャプチャして記録し、手頃な価格でエラーレポートを瞬時に取得することができます。これにより、設計およびテスト・エンジニアは開発時間を短縮し、市場投入までの時間のニーズに対応することができます。PCIe Gen4データは、ルートコンプレックスとエンドポイント(被試験デバイス)間のインターポーザを使用してキャプチャされます。PCIe Gen4プロトコルアナライザのソフトウェアは、トランザクションレイヤーパケット(TLP)、データリンクレイヤーパケット、およびLTSSM情報の完全なデコードとエラー解析を提供します。

主な特徴

- PCIe Gen1/2/3/4-X4プロトコルデコードおよび解析。

- 現在、4レーンのPCIeGen1/2/3/4 Busをサポート。

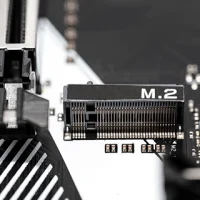

- アクティブM.2 PCIe Gen4までの速度に対応するコネクタインターポーザは、プロトコルアナライザとともに標準提供される。

- オプションのパッシブM.2 PCIe Gen3までの速度に対応するコネクターインターポーザー。

- オプションのソルダーダウンプローブチップは、PCIe Gen3(8Gbps)までの速度に対応する4レーン用

- TS1、TS2、TLP、DLLPパケットのプロトコル解読。

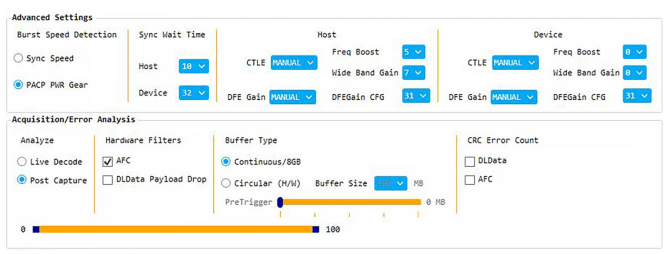

- ハードウェアベースのプロトコル・パケットTS1、TS2、IDLEフィルター機能。

- ソフトウェアベースの検索、フィルターイン、フィルターアウト機能。

- ハードウェアベースのプロトコル認識トリガー機能。

- 高度なマルチレベル if-then-else if トリガー機能。

- 標準バッファサイズは16GBで、TXとRXを合わせて64GBまで拡張可能。

- TS1、TS2、TLP、DLLPパケット内容に基づくトリガー。

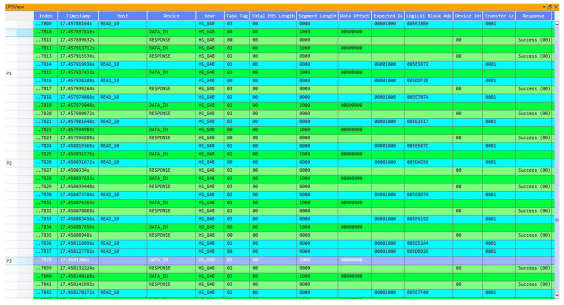

- 各TLP/DLLPの詳細表示と全フィールド値。

- PCIeプロトコルトラフィックのLTSSM解析。

- セグメントごとにトリガー条件が異なるメモリセグメンテーション¹。

- トリガー・イベント時のトリガー・アウト信号により、オシロスコープなど他の測定器のトリガーが可能。

- USB 3.0を使用したホストシステムとのインターフェース。

- デコードされたデータパケットは、さらに分析するために.txtファイルにエクスポートすることができます。

- PGYプロトコルアナライザーは軽量で、現場/フィールドテストに配置できる。

- フィールド・アップグレードが可能なため、最新の機能セットへのメンテナンスが容易。

1. 将来のリリースでサポートされる予定です。

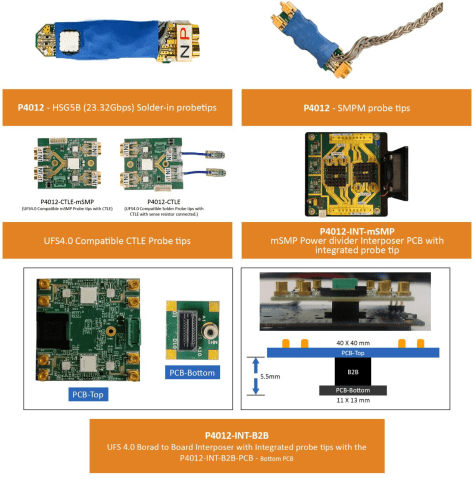

アクティブプローブをはんだ付けすることで、MPHYテストポイントのプロービングが可能になる。 これにより、設計およびテストエンジニアは、ホストとUFSメモリ間のUFSトラフィックを高い信号忠実度でキャプチャすることができます。 今日のテストエンジニアは、実際のユースケースを模倣したユースケースシナリオをラボでテストする必要がある。 PGY-UFS4.0-PA、UFSプロトコルアナライザは、エンジニアが様々なユースケースシナリオを実行しながら、ホストとデバイス間のトラフィックを詳細に監視、分析できるように設計されています。

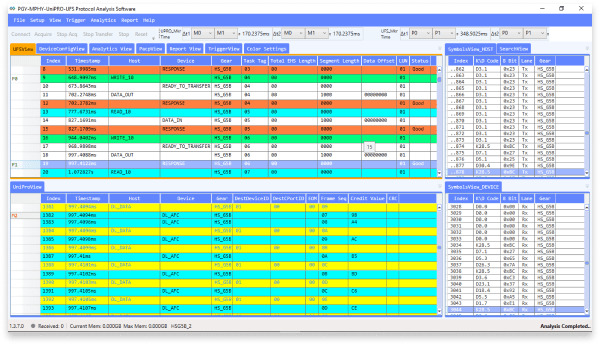

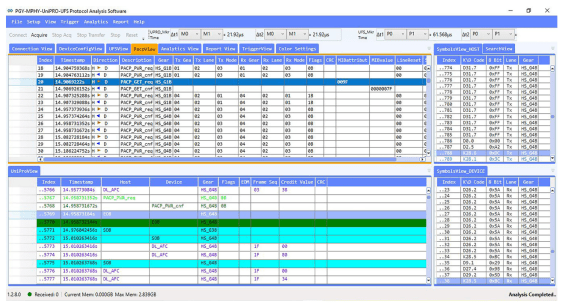

Windowsベースのプロトコル解析ソフトウェアは、UFSからUniPro、MPHYレイヤー間のプロトコル相関において業界最高水準を提供します。 異なるプロトコル層間の時間相関は、設計のデバッグ時間を大幅に短縮する。 このソフトウェアのフローティング・ウィンドウ・デザインにより、エンジニアはUFSビュー、UniProビュー、MPHYビューを異なるコンピューター・モニターで表示し、UFSパケットとMPHYレイヤーを自動的に関連付けることができる。 これにより、ギガバイト単位のプロトコル情報を分析するのが非常に簡単になる。

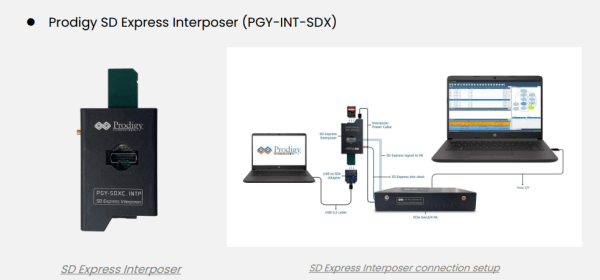

神童インターポーザー

PGY-UFS 4.0-PA UFSプロトコルアナライザーは、mSMP Flexi同軸ケーブルを使用して、ハンダダウンプローブチップに接続します。 アクティブ・プローブ・チップは、PGY-UFS4.0-PAから電源を供給されるパワーモジュールによって駆動される。 プロトコルアナライザは、USB3.0インターフェースを使用してホストコンピュータに接続されます。 高速ホスト接続と16GBのバッファにより、ホストSSDとストレージへのプロトコル・データの長時間連続ストリーミングが可能。 MPHYビュー、UniProビュー、UFSビューといったマルチビューを提供する。 各ビューには、デバッグしやすいように、各レイヤーの相関関係とともに、それぞれのプロトコル・パケットとその詳細が一覧表示される。 軽量なアナライザーは、現場視察の際に持ち運びが容易である。

UFSプロトコル層

PGY-UFS 4.0-PAソフトウェアでは、各UFSパケットパラメータを一覧ウィンドウで表示することができます。 右クリックすると、ユーザーが選択できるすべてのパケットパラメータが表示されます。 ユーザーは、各UFSパケットを簡単に識別できるように、フォントや背景色を色分けすることができます。

PACPとユニプロの見解

PGY-UFS4.0-PAソフトウェアは、パワーモード変更パケットとUniProパケットへのリンクを簡単に分析できるように、PACPパケットを別のビューに分離しています。 ユーザーは、DL_DataおよびAFC/NACKパケット詳細のユーザー選択とは別に、UniProビューでMPHYの状態失速、準備、同期情報を見ることができる。

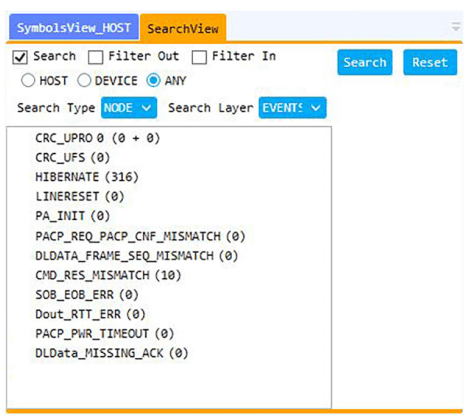

エラー・イベント、検索、フィルター

PGY-UFS3.X-PAソフトウェアはライブデコードを行い、すべてのイベントをリストアップします。 イベントのリストはこの写真の通り。 ユーザーは、キャプチャしたプロトコルデータのエラーを簡単に記録できる。 大規模なバッファーキャプチャでは、エラーの場所を特定するのは非常に難しい。 しかし、PPGGY-UFS3.X-PAソフトウェアは、キャプチャしたデータをデコードしながらイベントをリストアップすることで、これを簡素化する。 Search and Fliterは、プロトコルのリストウィンドウでエラーイベントやUFS、UniPro、PACPパケットを直接見つけることができます。 フィルターインとフィルターアウトにより、プロトコルのリストウィンドウで目的のデータを簡単に表示できる。

マルチビューによる包括的なプロトコル解析

PGY-UFS4.0-PA UFSプロトコルアナライザは、ホストコンピュータ接続用にUSB3.0インターフェースを提供します。 高速ホスト接続は、ホストHDDとストレージへのプロトコルデータの長時間連続ストリーミングを可能にする。 MPHYビュー、UniProビュー、UFSビューといったマルチビューを提供する。 各ビューには、デバッグしやすいように、各レイヤーの相関関係とともに、それぞれのプロトコル・パケットとその詳細が一覧表示される。

PGY Protocol Analyzerの使いやすいインターフェースは、プロトコル解析時間を短縮します。 プロトコル・デコード一覧のタイムスタンプ表示により、ホストとデバイス間のプロトコル・アクティビティを簡単に確認できます。 ボタンをクリックするだけで、ユーザーは各パケットのデコードと意図された機能を見ることができる。 フローティング・ウィンドウ・ソフトウェア・アーキテクチャにより、ユーザーは各プロトコル・レイヤーを別々のモニターに表示することができ、デバッグが容易になります。 UFS層からMPHY層まで、選択された各パケットの自己相関がデバッグ作業を簡素化する。

UFSプロービングソリューション

PGY-UFS4.0-PA UFSプロトコルアナライザは、ホストコンピュータ接続用にUSB3.0インターフェースを提供します。 高速ホスト接続は、ホストHDDとストレージへのプロトコルデータの長時間連続ストリーミングを可能にする。 MPHYビュー、UniProビュー、UFSビューといったマルチビューを提供する。 各ビューには、デバッグしやすいように、各レイヤーの相関関係とともに、それぞれのプロトコル・パケットとその詳細が一覧表示される。

PGY Protocol Analyzerの使いやすいインターフェースは、プロトコル解析時間を短縮します。 プロトコル・デコード一覧のタイムスタンプ表示により、ホストとデバイス間のプロトコル・アクティビティを簡単に確認できます。 ボタンをクリックするだけで、ユーザーは各パケットのデコードと意図された機能を見ることができる。 フローティング・ウィンドウ・ソフトウェア・アーキテクチャにより、ユーザーは各プロトコル・レイヤーを別々のモニターに表示することができ、デバッグが容易になります。 UFS層からMPHY層まで、選択された各パケットの自己相関がデバッグ作業を簡素化する。

仕様

Data Rates Supported | PCIe Gent, Gen2, Gen 3, Gen 4. (with Option PCIe4) |

Link Width | Four lanes (Four TX and Four RX). |

Probes | Active M.2 Interposer (Standard) Solder Down Active Probes for speeds up to PCIe Gen3.(optional) |

Protocol Decode | TSL TS2, TLP, DUP SOS, IDLE, EIOS, EIEOS, FTS, SKP |

Trace Capture Size | Supports Continuous streaming of Protocol data to Host computer SSD/HDD. And Post Capture up to buffer size. |

Trigger | Based on TST TS2, TLP, DLLP. |

Connectors | Interface for Active probes. Trigger in/out SMA connectors. |

Interface for Host Computer | USB 3.0 |

Host Computer Requirements | Processor: Intel i7 10" Generation or better (Equivalent) Operating System: Windows 7/8.0/81/10 64bit OS RAM: minimum 1608 but the product would give a faster response for 3208/6408/more. Storage: 25608 SSD or more (minimum storage capacity of 108 should be available in the hard disk drive. User can use more storage based on trace storage requirement) Display resolution: 1024x768 Interface: Host computer should support USB 3.0 interface |

Dimension (WxHxD) | (WxHxD) (205x5x25) cms. |

Weight | Approx 4 kg |

Power Requirement | 12V 6A DC Power Supply (AC/DC Supplied along with Analyzer). |